Cadence unveils partner ecosystem at CES 2026 to fast-track chiplet-based physical AI systems. The initiative targets data centers, HPC, and edge devices like robots and vehicles. It promises quicker market entry through pre-verified components.

Key Ecosystem Features

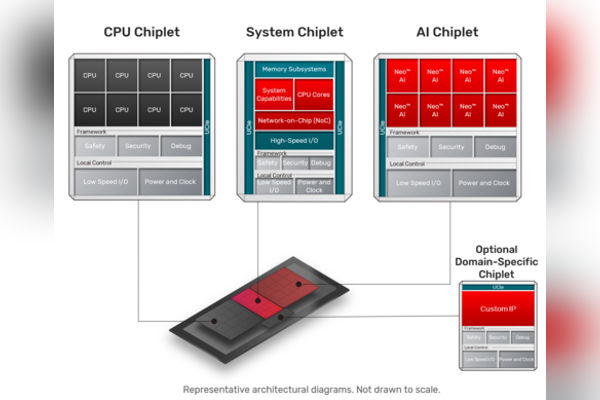

Cadence’s spec-to-packaged parts approach automates chiplet frameworks with built-in management, security, and safety tools.

Developers gain seamless EDA flows for simulation via Xcelium and emulation on Palladium Z3 platforms. Physical designs benefit from real-time optimization for efficient layouts.

Initial collaborators feature Arm for Zena CSS integration, alongside Arteris, eMemory, M31 Technology, Silicon Creations, and Trilinear for IP. ProteanTecs adds silicon analytics, while Samsung Foundry supports SF5A prototypes with pre-integrated IP.

Standards like UCIe, Arm CSA, and future OCP ensure wide compatibility for interfaces including PCIe 7.0 and HBM4.

Cadence will continue to collaborate closely with Arm, utilizing its cutting-edge Zena Compute Subsystem (CSS) and other crucial intellectual property for the chiplet architecture and physical AI platform.

The new solutions will satisfy standards-based I/O and memory chips for data center, cloud, and HPC applications, as well as edge AI processing requirements for autos, robotics, and drones.

The chiplet ecosystem provides spec-driven automation to create chiplet framework architectures that integrate advanced software, security, safety features, and Chiplet management with Cadence and third-party partner intellectual property.

The company stated that the physical design flow uses real-time input for effective place-and-route cycles, while the resulting EDA tool flow allows simulation with the Cadence Xcelium Logic Simulator and emulation with the Cadence Palladium Z3 Enterprise Emulation Platform.

Key Comments

Key Comments

“Cadence’s latest chiplet ecosystem marks a pivotal achievement in chiplet facilitation,” said a Cadence Compute Group vice president. “Our offerings optimize expenses, deliver customization, and enhance configurability by merging IP with partner networks to reduce risks.”

ProteanTecs’ head of business noted, “We’re excited to partner with Cadence on embedding telemetry across chiplet types for safe, reliable physical AI.” An earlier Cadence system chiplet prototype passed full silicon validation.

To Know More: CLICK HERE