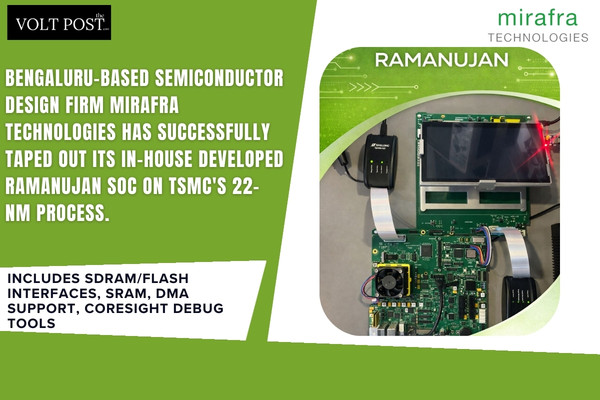

Bengaluru-based semiconductor design firm Mirafra Technologies has successfully taped out its in-house developed Ramanujan SoC on TSMC’s 22-nm process, marking a key step in proving full end-to-end silicon capabilities.

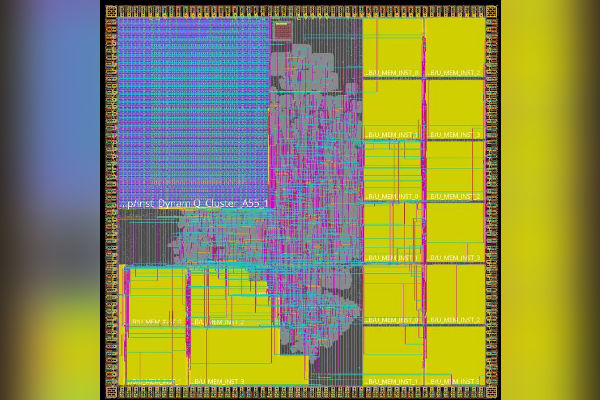

This internal project showcases a modular architecture with dual network-on-chip (NoC) designs, separating app processing via an Arm Cortex-A55 core from secure system functions using an InCore RISC-V Azurite core.

It includes SDRAM/Flash interfaces, SRAM, DMA support, CoreSight debug tools, and peripherals for IoT and industrial uses, validated through FPGA prototyping with a Linux software stack demoed at VLSI Design Conference 2026.

Mirafra Technologies’ Ramanujan is a 22-nm SoC fabricated at TSMC, designed as a modular IoT/industrial reference platform with dual network-on-chip (NoC) architecture separating app processing from secure/system functions.

Core Processors

Core Processors

- Single-core Arm Cortex-A55 for application tasks, leveraging modern enhancements for efficiency and multitasking.

- InCore RISC-V Azurite core dedicated to system management, secure boot, and control.

Memory and Interfaces

- External support: SDRAM, Flash, HyperRAM.

- On-chip SRAM with DMA for data movement.

- Mix of high-speed/low-speed peripherals; clock/power management blocks.

Additional Features

Includes CoreSight debug/test infrastructure, scan chains, memory BIST for high coverage, and in-house IP where needed; validated via FPGA with Linux/multimedia stack. Lacks analog/power drivers or image processing for general-purpose focus.

Key Comments

Key Comments

Mirafra’s co-founder and CEO Alok Kuchlous emphasized the project’s goal, “This demonstrates our ability to own complete SoC programs from architecture to validation, aiding India’s fabless ecosystem under DLI/PLI schemes.” He added that Ramanujan serves as a customizable reference for OEMs, positioning the firm competitively on price and capability without entering merchant chip sales.