Under the DARE Project, the EuroHPC Joint Undertaking (JU) and member states provided up to €61.6M in funding to Axelera AI, a company that specializes in AI hardware acceleration technologies.

In order to create a RISC-V AI chiplet for high performance computing (HPC) applications, Dutch chip maker Axelera AI has raised this fund.

Pivotal Emphasis of DARE Program

To promote a competitive high-performance computing environment, the EuroHPC JU was established with the goal of developing, growing, and maintaining a unified supercomputing and quantum computing infrastructure.

In order to assist the EuroHPC JU in creating a European supercomputing ecosystem, Axelera AI is a member of the DARE consortium. European processors, accelerators, and associated technologies for high-performance and cutting-edge applications are the main emphasis of the DARE program.

The New Titania Chiplets in RISC-V Open Instruction

Multiple Titania chiplets will be bundled in a System-in-Package (SiP), and Axelera AI can quickly develop in response to changing customer needs by utilizing the RISC-V open instruction set architecture with vector extensions.

The fund will go toward the creation of Titania, a chiplet for AI inference intended for computing applications. The company’s Digital In-Memory computer (D-IMC) architecture, upon which the chiplet is built, allows for scalability in a variety of computer contexts.

With inference driving the majority of growth, the AI market is growing at a compound annual growth rate (CAGR) of over 28%. Concerns regarding the performance, affordability, and sustainability of cloud solutions are growing as new AI models need more processing power.

To overcome these obstacles, Axelera AI intends to implement Titania in 2028. It seeks to increase throughput and efficiency for high-performance computing facilities and AI applications. The business will increase its research and development teams in Belgium, Italy, and the Netherlands to help in this endeavor.

The Titania chiplet-based architecture from Axelera AI will integrate RISC-V capabilities with D-IMC technology to meet the increasing demands of AI in industries including robotics, automotive, data centers, and high-performance computing.

Leadership Comments

Anders Jensen, EuroHPC JU Executive Director, says, “I am proud to announce the launch of the DARE project which marks a significant milestone for European digital sovereignty. This ambitious initiative will drive innovation in both hardware and software technologies and leverage the full power of HPC and AI to develop secure, efficient and European-led solutions for the future.”

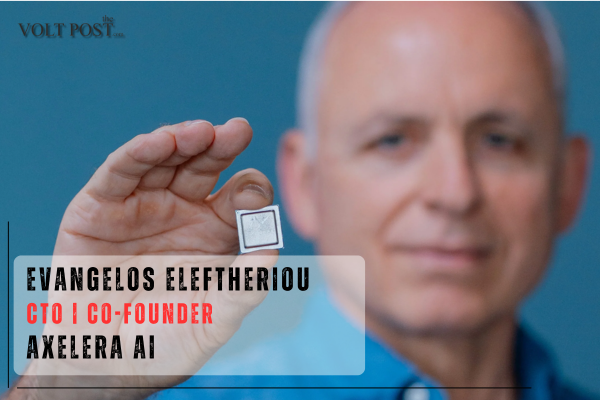

Evangelos Eleftheriou, CTO and Co-Founder of Axelera AI, says, “Our D-IMC technology leverages a future-proof, scalable multi-AI-core architecture, ensuring unparalleled adaptability and efficiency. Enhanced with proprietary RISC-V vector extensions, this versatile mixed-precision platform is engineered to excel across diverse AI workloads.”

“Uniquely, our architecture facilitates scaling from the edge to the cloud, streamlining expansion and optimising performance in ways that traditional cloud-to-edge approaches cannot. We are setting a new standard for AI infrastructure, making true scalability a tangible reality.”